ПАКТИКУМ З ЦИФРОВОЇ ЕЛЕКТРОНІКИ

Анотація

Анотація

|

Логічні елементи

Логічні елементи

|

Тригери, Лічильники

Тригери, Лічильники

|

Цифрові перемикачі, Регістри

Цифрові перемикачі, Регістри

|

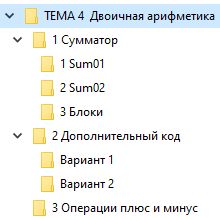

Бінарна арифметика

Бінарна арифметика

|

АЛП, Скінченні автомати

АЛП, Скінченні автомати

|

Основна мета сторінки це надати ряд прикладів, які можуть полегшити самостійне опанування основ цифрової схемотехніки. Приклади, розроблялися як наочний матеріал до лабораторних робот, що входили до складу ряду навчальних курсов нашої кафедри. Особливо необхідно підкреслити, що заради логічної прозорості, практично всі наведені схеми представлені без оптимізації логіки їх побудови.

|

Рекомендована література

Для початку дамо посилання на офіційну та довідкову документацію необхідну для дослідження та проектування цифрової сземотеніки. Також, для зручного знайомства з цифровою електронікою, наведемо декілька важливих документів:

|

На сьогодні вже відома значна кількість систем моделювання електроніки. Але історично так склалося, що коли на початку 2000 року виникла для навчального процесу потреба в моделюванні електроних та електротехнічниних схем, відносно доступною виявилася система WORKBENCH. В подальши часи фірма National Instruments підтримала розвиток цього напрямку серією систем Multisim.

Всі наведені на сторінці моделі представлені в Multisim версії 11 (в окремих випадках також в версії 8). Моделі спроектовані в Multisim верии 11 без проблем імпортуються в Multisim версії 14. |

ЕЛЕМЕНТИ:

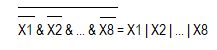

Наприклад, закон де Моргана, який встановлює зв'язок між операціями NOT, OR

та AND, дозволяє зрозуміти чому лише єдина операція OR-NOT (Стрелка Пирса)

або AND-NOT (Штрих Шеффера) дозволяють реалізувати операції NOT, OR та AND,

а далі і всю логічну алгебру. Як цікавий схемотехнічний приклад можна

навести наступе:

Комбінаційні схеми. Комбінаційні схеми можна визначити як схемотехнічна реалізація простих або складніх логічних виразів, що включають в себе лише операції NOT, OR, AND та їх комбінації . Зазвичай до комбінаційних схем відносять різноманітні шифратори та дешифраторі кодів, а також реалізацію логічних або арифметичних функцій.

Наприклад:

Другий приклад стосується реалізації арифметичної функції:

|

ФКІ та ГЕНЕРАТОРИ:

операція OR-NOT (.jpg)

), або

протигоночним кодуванням сигналів, тобто вибором такого кодування, коли одночасно

змінюється лише один сигнал (типово застосовується в схемотехниці кінцевих

автоматів).

операція OR-NOT (.jpg)

), або

протигоночним кодуванням сигналів, тобто вибором такого кодування, коли одночасно

змінюється лише один сигнал (типово застосовується в схемотехниці кінцевих

автоматів).

ФКІ. Якщо кожна " медаль має зворотний бік ", то гонка сигналів також може слугувати

для реалізації користних схем. До числа таких сжем можна віднести формувачі коротіх імпульсі

по обраному фронту вхідного сигнала (ФКІ) та генератори імпульсів на затримках.

Як приклад ФКІ наведемо Генератори. В цьому підрозділі розглянуто моделі генераторов прямокутних імпульсів стабільність частоти яких не потребує високих вимог. Нажаль моделі стабільних генераторів з кварцевими резонаторами змоделювати в MultiSim не вдається, якщо в схемах застосовується лише логічні елементи. Тому класичні кварцові генератори на логічних елементах винесені за дужки.

Самий простий генератор можна реалізувати на двох RC-затримках (С2 >= С1) та інверторами

з тригерами Шмідта, що забеспечує чітке реагування на похилий фронт на виході RC-ланцюжків.

Також простий генератор можна реалізувати на двох ФКІ. Така реалізація дозволяє незалежно

обирати довжину імпульса та паузи. Якщо необхідно встановити довгу паузу, то ії краще

формувти за допомогою таймеру серіі 555.

Якщо вам необхідно створити максимально стабільний генератор без застосування кварцеого

резонатору, то добрим рішенням буде використання таймеру серіі 555. Це обумовлено тим, що

рівень напруг для кордонів логічної одиниці або нуля визначається в таймері точними

аналоговими компораторами. Таким чином, стабільнісь такого генератора буде залежна лише

від стабільності пасивних елементів (резисторів та конденсаторів) |

ТРИГЕРИ:

Тригер має два входи (set-установка вихода Q в одиницю та reset-установка вихода Q в в нуль. Визначимо вхідні комбінації для такого тригера:

Комбінації: --> (set=0, reset=1) --> (set=1, reset=1)

Розглянемо установку вихода тригера Q в одиницю, тобто

(set=0, reset=1). Сигнал (set=0) призведе до того, що

на виході елементу Е1 буде встановлена одиниця незалежно від того який

сигнал X буде на другому вході елемента Е1. Дійсно,

(вихід Е1) = not (0 and X)=1. Не важко здогадатися, якщо схема тригера дзеркальна відносно елементів Е1 та Е2, то установка тригера, сигналом (set=1, reset=0) має вже розглянуту логіку, а комбінація (set=1, reset=0) це дійсно утановка вихода тригера Q в нуль. Проблема комбінації: (set=0, reset=0) --> (set=1, reset=1) Але особливо необхідно розглянкти реакцію тригера на перехід від забороненої вхідної комбінації (set=0, reset=0) до комбінації збереження (set=1, reset=1). Типово, такі переходи виникають коли вмикаєтся живлення приладу, або якщо попередня логіка, що формує сигнали на входах тригера, має різні затримки та здатна формувати короткочасні проміжні сигналі (детально ми розглядали це в розділі ЛОГІЧНІ ЕЛЕМЕНТИ). Проблема переходу від (set=0, reset=0) до (set=1, reset=1) полягає в тому, що не можна визначити в якому стані буде завершено такий перехід, тобто невідомо одиниця чи нуль залишаться на Q-виході тригера. Дійсно, після комбінації (set=0, reset=0) на виходах Е1 та Е2 примусово утворюються одиниці, а при включенні комбінації (set=1, reset=1) оба елемента Е1 та Е2 мають перейти в стан нуля, що дзеркально змінюе ситуацію. Тому невідомо, який з елементів встигне швидше виконати переключення та відповідно виграти гонку переключень. В окремих (дуже рідких випадках) внутрішні затримки настільки ідентичні що починається безперервна генерація. В папці (1 Триггеры и Счетчики\1 Триггеры\1 RS-Триггер\2 Проблемы) можна знайти відповідні моделі. Вирішення проблеми переходу (set=0, reset=0) --> (set=1, reset=1)

У випадку вмикання живлення, та і в інших багатьох випадках, коли необхідна початкова

утановка схеми, в тригери влючаеться додатковий вхід з назвою СКИНУТИ, скорочено

CLN або CLR (clean або clear).

Таку модифікацію тригера у найвпрстішому вигляді можна зобразити наступним чином:

У випадку різноманітних затримок вхідних сигналів, единим гарантованим рішенням є дочекатися коли всі затримки закінчаться і лише потім дозволити сигнали установки тригера. Таке рішення мпє назву СИНХРОНІЗАЦІЯ, а відповідні тригери називаються синхроними. Синхроні тригера, в свою чергу, поділяют на однотактні та двотактні. Однотактні тригера змінюють свій стан відразу, коли з'являється сигнал сінхронізації, а двотактні змінюють свій стан коли сигнал синхронізації завершується, тобто в кінці імпульса синхронізації.

Розглянемо найпростіше схемотехнічне рішення однотактного синхроного RS-тригера:

|

Схема найпростішого двотактного синхроного RS-тригера наведена на малюнку;

Крім того, двотактний синхроний RS-тригер легко модифікуються в найпростіший:

Заключний коментар з приводу синхронізації Якщо ми маємо декілька скінченних автоматів (спрощено, схем з тригерами та комбінаційною логікою на входах та виходах) що включені послідовно, то нам, скоріше за все, знадобится щось накшталт многофазного гекератора коротких імпульсів (такі генератори ми вже розгядали в розділі ФКІ та ГЕНЕРАТОРИ). Послідовно в часі тактові імпульси таких генераторів дають змогу дочикатися поки сигнали на входах тригерів набудуть завершеного вигляду для кожного автомату. D-, JK- ТРИГЕРИ:

D-тригер є логічною модифікацією двотактного синхронного RS-тригера. Найпростішу

логічну схему D-тригера ми вже фактично розгядали, коли входи двотактного синхронного

RS-тригера об'єднали з допомогою інвертора в один вхід з назвою D, надавши йому сенсу

вхідні данні (data).

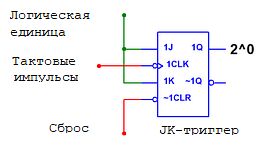

JK-тригер також можна розглядати, як логічну модифікацію двотактного синхронного

RS-тригера. Типово тригер має три входи: тобто CLK, J (Jump) швидке вмикання та K (Kill)

швидке вимикання. При (J=K=1) JK-тригер працює як двотактний Т-тригер. При (J=0, K=1) або

(J=1, K=0) JK-тригер працює як двотактний RS-тригер, де вход J аналогічен S входу RS-тригера,

а вход K аналогичен входу R. При (J=0, K=0) тригер не реагує на імпульси CLR та зберігає

поточний стан, тобто JK-тригер не має заборонених вхідних комбінацій. Хоча JK-тригер

позиціанується як універсальний, для реалізації на його бізі D-тригера необхідно додати

зовнішній інвертор з входу J на вхід К. Заключний коментар з приводу тригерів

На цій сторінці ми розглянули структуру та логіку найбільш вживаних в схемотехниці тригеров,

при цьому (для логічної прозорості) винесли за дужки оптимізацію структри в прикладах.

До речі, в архіві розглянуто значна кількість моделей відображаючих різноманітні

модифікації тригеров. Додаткову інформацію можна отримати з огляду тригерів на вікопедії:

T-ТРИГЕРИ, ЛІЧИЛЬНИКИ ІМПУЛЬСІВ: Базовим елементом лічильників можна важати T-тригери. На малюнку, що наведений нижче, показанно модифікації JK- та D-тригерів у T-тригер.

Особливостю T-тригера є зміна його стану з нуля в одиницю або навпаки на кожний тактовий імпульс, тобто період сигналу на виході T-тригера в два рази довший ніж реріод тактових імпульсів. Якщо створити ланцюжок з Т-тригерів такий, що вихід попереднього тригера (Q) приєднується к тактовому входу (CLK) наступного тригера, то на виходах тригерів ланцюжка кожний наступний тактовий імпульс буде послідовно формувати бінарних код. На малюнку, що наведений нижче, показана відповідна осцилограма для лічильника прямого рахунку (модифікація з JK-тригерами).

Тобто, осцилограма ілюструе роботу лічильника із зростаючим бінарним кодом полубайтової

разрядності. Але, якщо застосувати в ланцюжку інверсні виходи Т-тригерів, то бінарний код

буде змінюватися вже не у прямому, а в зворотньому напрямку. Перемикання між напрямком рахунку

можна виконати дуже простими комбінаторними схемами і, в такому випадку, ми отримаємо

універсальний (реверсійний) бінарний лічильник. Модеді таких найпростіших лічильників

наведені в папці (1 Триггеры и Счетчики\2 Счетчики) в складі архіву. В професійних рішеннях

ревесівних лічильників зазвичай також застосовується входи тригерів PR (Data Propagation

delay/Затримка передачі даних), але ми разглядаємо лише логіку, тобто, у випадку реальних

схем, зімість наведених прикладів, використовуються мікросхеми, де питання тонкої

синхронізації вже врегульовані (наприклад, 74161N, 74F161AN, 74LS161N та інші).

Важливою модифікацією бінарних лічильників можна разглядати лічильники з довільною основою

рахунку, тобто, із основою рахунку 3, 5, 6, 7, 10, 12 та інше). В найпростішому випадку

застосовуються відповідні дешифратори бінарного коду (тобто 3, 5, 6, 7, 10, 12 та інше), які

відслідковують вихідний код бінарного лічильника та коли він досягає основи рахунку формують

сигнал сбросу на асинхронний вхід лічильника. Тобто, замість переходу до коду основи рахунку

лічильник повертається до коду нуля. В професійних рішеннях бажано, щоб тривалість імпульсу

сбросу дорівнювала тривалісті тактового імпульсу. Нійбільш популярними мікросхемами лічильників

з довільною основою рахунку є бінарно-десятичні лічильники (наприклад 74192N, 74F192N,

74LS192N та інші), які відображають кожну десятичну цифру у бінарному коді, наприклад: Інші приклади побудови розглянутих лічильників наведені в папці (Триггеры и Счетчики\2 Счетчики\2 Примеры) в складі архиву. |

ЦИФРОВІ ПЕРЕМИКАЧІ:

ДЕМУЛЬТИПЛЕКСОРИ: Модель для тестування демультиплексора наведена в папці (ТЕМА 3 Переключатели Регистры\1 Переключатели\Логика\1 Демультиплексор)

МУЛЬТИПЛЕКСОРИ:

Моделі для тестування мультиплексорів наведені в папках (ТЕМА 3 Переключатели Регистры\1 Переключатели\Логика\2 Мультиплексор\Вариант1) та (ТЕМА 3 Переключатели Регистры\1 Переключатели\Логика\2 Мультиплексор\Вариант2) |

РЕГІСТРИ:

ПАРАЛЕЛЬНІ РЕГІСТРИ: Основне застосування паралельних регістрів це буферізація даних (типово байту або полубайту), а також фіксація стану бітів комбінаційних схем або скінченних автоматів з затримкою на завершення перехідних процесів. Модель для тестування паралельного регістру наведена в папці (ТЕМА 3 Переключатели Регистры\2 Регистры\1 Параллельные\1 Логика)

РЕГІСТРИ ЗСУВУ:

Основне застосування регістрів зсуву це перетворення послідовного код в

паралельний код або навпаки, а також виконання допоміжних мікрооперацій

в арифметичних або логічніх операціях. Наприклад, спощена: До регістрів зсуву можна також віднести ПЗЗ, тобто прилади із зарядовим зв'язком (англ. CCD, charge-coupled device), в яких застосовується технологія керованого перенесення заряду в об'ємі напівпровідника.

Напрямок зсуву заряду визначається динамікою потенціалів на керуючих

електродах Е1,Е2,Е3.

РЕГІСТРИ З ТРЬОМА СТАНАМИ:

РЕГІСТРИ ЗАСУВКИ (Latch):

Приклад побудови регістра засувки наведена в моделі: |

Моделі в архіві реалізовані в Multisim версії 11. Кожна супроводжується електричною схемою в форматі pdf.

У рамках WEB-сайту дуже важко докладно представити логіку побудови та реалізацію пристроїв комп'ютерної електроніки. Тому ми зупинимося тільки на ключевих моментах, які в подальшому полегшать знайомство з цим напрямком науки та технології.

Бінарні обчислення:

Зазначимо, що негативне та позитивне число з однаковими модулями є дзеркальним відображення відносно нуля, тобто пустого заначення в вмножині чисел. Також необхідна доступність операцій для побудови алгоритмів, тобто:

Ми навели дуже спрощені алгоиритми множення та поділу лише для цілих чисел,

але (без додаткової деталізації) зазначимо, що дійсні числа за допомогою

масштабних коефіцієнтів можна перетворити в цілі числа, виконати операцию, а потім

зробити зворотне масштабне перетворення. Також зазначимо, що на даний час розроблено

значна кількість алгоритмів множення та поділу чисел, наприклад:

Звісно, вище наведені лише значно спрощені алгоиритми множення і поділу двох чисел, більш того, лише для цілих чисел. А як же дійсні числа? Без додаткової деталізації зазначимо, що дійсні числа за допомогою масштабних коефіцієнтів можна перетворити в цілі числа, виконати операцию, а потім зробити зворотне масштабне перетворення.

Підіб'ємо деякий підсумок. Якщо ми маємо операції додавання, віднімання, множення та

поділу числел, то наступними алгоритмічними кроками буде створення операцій "піднесення

в цілий ступінь", "факторіал", а також реалізація широкого переліку функцій, що вже

розглядалося в

Визначення об'єкта "позитивне бінарне число" та цого базових операцій

Xn * 2^n + ... + X1 * 2^1 + X0 * 2^0 |

Операція суми двох бінарних чисел

Ri = (Xi xor Yi) xor Ci

За посиланнім наведемо приклад

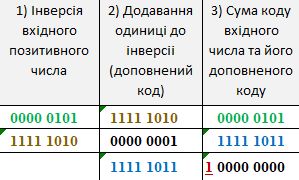

Операції зміни знака числа

З наведеного прикладу ми бачимо - якщо ігногувати біт переноса (червона підкреслена одиниця), то контрольна сума для пошуку негативного коду буде дорівнювати нулю. Таким чином побітова інверсія вхідного коду с додаванням одиниці, дійсно утворюе негативний код вхідного позитивного числа. Такий код отримав назву "Додатковий/Two’s complement" або в, деяких джерелах, як "Доповнювальний".

В архіві, у папках розділу, наведена модель

З наведеного прикладу ми бачимо - якщо ігнорувати біт переноса (червона підкреслена одиниця), то контрольна сума для пошуку негативного коду буде дорівнювати нулю. Таким чином побітова інверсія вхідного коду с додаванням одиниці, дійсно утворюе негативний код вхідного позитивного числа. Такий код отримав назву "Додатковий/Two’s complement" або в, деяких джерелах, як "Доповнювальний". З основ загальної математики нам відомо, що абсолютне значення позитивного числа та абсолютне значення того же числа со знаком мінус мають одне значення. В комп'ютерній арифметиці абсолютне значення числа со знаком має назву "Модуль числа". Якщо значення модуля позитивного числа дорівнюе значенню самого числа, то дзеркальна (відносно нуля) властивость модуля дозволяе отримувати значення модуля негативних чисел за допомогою поразрядної інверсії додаткового коду з додавання одиниці. Наведемо приклад отримання модуля додаткового бінарного коду десятичного числа п'ять:

На завершення буде корисно неквапливо дослідити бінарні операції плюс та мінус

з целими числами за допомогою моделі, що представлена в розділі архіва:

Для подальшої деталізації теми розділу буде корисним перегянути wiki - посилання

на:

|

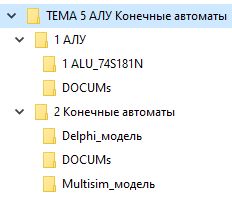

Моделі в архіві реалізовані в Multisim версії 8 та 11, а також як програми на Delphi. Кожна супроводжується електричною схемою в форматі pdf.

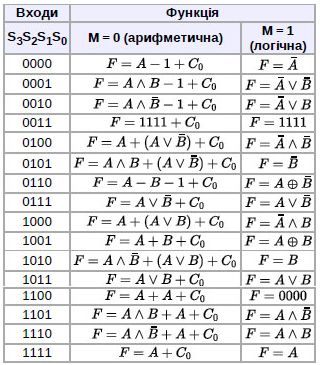

АЛП: В розділі 4 ми вже перераховували операції, які необхідні для комп'ютерної арифметики цілих чисел, але в наведених моделях показали лище реалізацію операцій плюс, мінус, модуль. В даному розділі наведемо пристрій 74S181N, в якому додано логічні операції та збільшено кількість арифметичних операцій:

Такий пристрій отримав назву арифметико-логічний (АЛП), а його реалізація

представлена, як

Центральний процесор: Сьогодні найбільш повний вигляд, як складу операцій, так і алгоритмів їх реалізації, пропонують пристрої, що отримали назву "Центральний процесор, ЦП (англ. Central processing unit, CPU)". Більшисть операцій в процесорах виконується алгоритмічно (мікропрограмно), та в завершенному вигляді мають назву "інструкції" або "команди". Процесори (с позиції цифрової електроніки) мають дуже складну структуру, тому, як правило, їх опис включає загальну архітектуру, що включає в себе архітектуру команд. На сьогодні, до найбільш відомих архітектур процесорів можна віднести:

Всі сучасні процесори мають розвинені можливості обслуговування переривань,

роботи з оперативною пам'яттю, шинами адреси та шинами даних. Та окремим рядком

треба відначити здатність сучасних процесоров паралельно виконувати інструкції.

Така особливость архітектури процесора отримала назву Суперскалярність

Детальний опис архітектури процесорів потребує, як мінімум, книги з великою

кількістю сторінок, а то і декілька таких книг. Наприклад, тільки скорочена

довідка по архитектурі x86 має вже помітно значний обсяг. Тому, для досягнення

професійного рівня усвідомлення матеріалу використовуйте літературу, надану

в wiki-посиланнях. В україномовній Вікіпедії корисни буде посилання:

Зрозуміло, що окремо від обчислювальної системи процесор є не більше,

чим просто електронна мікросхема або пристрій. Тому на завершення розділу

наведемо, як приклади окремих мікропроцесорів, так и відносно простих

обчислювальних систем, таких як персональні комп'ютери (ПК):

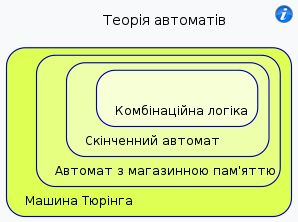

СКІНЧЕННІ АВТОМАТИ: В рамках цьго розділу ми зосередим увагу на лише скінченних автоматах, що призначені для керування об'єктами з кінцевою кількістю станів. Такі автомати допомагають розв'язувати багато задач, серед яких автоматизація проєктування електронних приладів, проєктування комунікаційних протоколів, синтаксичний аналіз та інші інженерні застосування. |

Скінченний автомат (англ. finite-state machine), автомат зі скінченною множиною станів це:

Проектування скінченного автомату починається з визначення кількості і сенсу його станів. Як правило, окремим станом об'єкта вважається ситуація, коли керуючому автомату для успішного керування об'єктом нема необхідності відстежувати інший перелік вхідної інформації та змінювати склад керуючих дій. Саме тому, типовий опис автомата, як мінімум, включає три таблиці:

До класичних скінченних автоматов традиційно відносять два типи автоматів:

В якості приклада реалізації скінченного автомату, наведемо

автомат для керування аналоговою частиною

Представлена логіка роботи АЦП, дозволяє виділити чотири стани в роботі АЦП, тобто, начальний стан, стан інтегрування вимірюваної напруги, стан інтегрування напруги опорного джерела, а також стан зупинки для фіксації результату.

Подальше проектування будемо виконувати відповідно до послідовності, що

пропонує

Як резултат проектування, ми отримаємо:

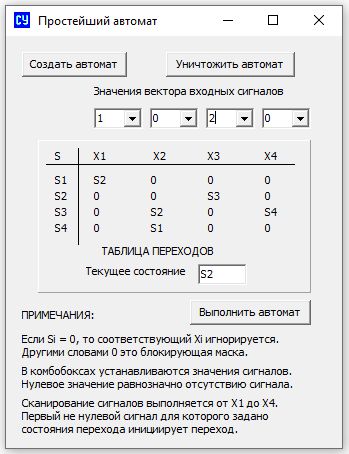

У методиці проектування таблиць автомату, пунктами 8 ... 10 було показано, що ідеологію скінчених автоматів можна застосовувати у комп'ютерних програмах. На малюнку представлена діалогова форма програми, де засобами ООП Delphi розроблено автомат з програмно завантаженими таблицями.

На завершення розділу зазначимо, що програмно реалалізовані автомати із вбудованою або додатковою стековою пам'яттю - це важливі елементи а архітектурі компіляторів, планувальників та диспетчерів виконання програм, модулів та об'єктів. |

Portal:Electronics

Portal:Electronics